# ADM6999G/GX

8 port 10/100 Mb/s + Gigabit Single Chip Ethernet Switch Controller

Communications

Never stop thinking.

#### Edition 2005-11-25

Published by Infineon Technologies AG, St.-Martin-Strasse 53, 81669 München, Germany © Infineon Technologies AG 2005. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

## Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

#### 8 port 10/100 Mb/s + Gigabit Single Chip Ethernet Switch Controller

Revision History: 2005-11-25, Rev 1.31

| Previous Ve | Previous Version:                                                                                                               |  |  |  |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Page/Date   | Subjects (major changes since last revision)                                                                                    |  |  |  |  |  |  |

| 2002-08     | Rev. 0.1: First ADMtek version                                                                                                  |  |  |  |  |  |  |

| 2002-09     | Rev. 1.0: Remove Preliminary word                                                                                               |  |  |  |  |  |  |

| 2002-12     | Rev. 1.1: Modify error word; Add GMII timing                                                                                    |  |  |  |  |  |  |

| 2003-04     | Rev. 1.2: Modify GMII receive setup time and hold time. GRXER change to GND or NC. Modify MII RXCLK & TXCLK timing requirement. |  |  |  |  |  |  |

| 2003-05     | Rev. 1.3: Modify RTX to 1K 1% at A2 version chip                                                                                |  |  |  |  |  |  |

| 2005-05     | Rev. 1.31: Changed to the new Infineon format                                                                                   |  |  |  |  |  |  |

| 2005-11-25  | Minor change. Included Green package information                                                                                |  |  |  |  |  |  |

|             |                                                                                                                                 |  |  |  |  |  |  |

|             |                                                                                                                                 |  |  |  |  |  |  |

## **Trademarks**

ABM®, ACE®, AOP®, ARCOFI®, ASM®, ASP®, DigiTape®, DuSLIC®, EPIC®, ELIC®, FALC®, GEMINAX®, IDEC®, INCA®, IOM®, IPAT®-2, ISAC®, ITAC®, IWE®, IWORX®, MUSAC®, MuSLIC®, OCTAT®, OptiPort®, POTSWIRE®, QUAT®, QuadFALC®, SCOUT®, SICAT®, SICOFI®, SIDEC®, SLICOFI®, SMINT®, SOCRATES®, VINETIC®, 10BaseV®, 10BaseVX® are registered trademarks of Infineon Technologies AG. 10BaseS™, EasyPort™, VDSLite™ are trademarks of Infineon Technologies AG. Microsoft® is a registered trademark of Microsoft Corporation, Linux® of Linux Torvalds, Visio® of Visio Corporation, and FrameMaker® of Adobe Systems Incorporated.

## **Table of Contents**

## **Table of Contents**

|             | Table of Contents                             | . 4 |

|-------------|-----------------------------------------------|-----|

|             | List of Figures                               | . 6 |

|             | List of Tables                                | . 7 |

| I           | Introduction                                  | . 8 |

| 1.1         | General Description                           | . 8 |

| 1.2         | Features                                      | . 8 |

| 1.3         | Applications                                  | . 9 |

| 2           | Input and Output Signals                      | 10  |

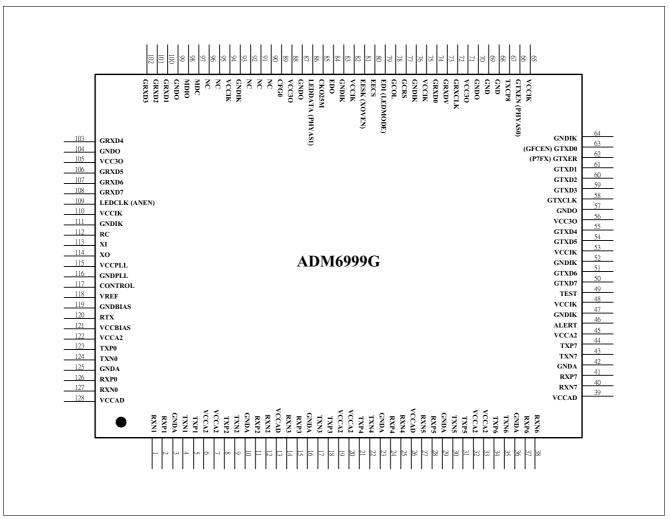

| 2.1         | Pin Diagram                                   |     |

| 2.2         | Pin Type and Buffer Type Abbreviations        |     |

| 2.3         | Pin Descriptions                              |     |

| 2           | Descriptions                                  | 17  |

| <b>3</b> .1 | Functional Description                        |     |

| 3.2         | 10/100M PHY Block Description                 |     |

| 3.2.1       | 100Base-X Module                              |     |

| 3.2.2       | 100Base-X Receiver                            |     |

| 3.2.2.1     | A/D Converter                                 |     |

| 3.2.2.2     | Adaptive Equalizer and Timing Recovery Module |     |

| 3.2.2.3     | NRZI/NRZ and Serial/Parallel Decoder          |     |

| 3.2.2.4     | Data De-scrambling                            |     |

| 3.2.2.5     | Symbol Alignment                              |     |

| 3.2.2.6     | Symbol Decoding                               |     |

| 3.2.2.7     | Valid Data Signal                             |     |

| 3.2.2.8     | Receive Errors                                | 19  |

| 3.2.2.9     | 100Base-X Link Monitor                        | 19  |

| 3.2.2.10    | Carrier Sense                                 | 20  |

| 3.2.2.11    | Bad SSD Detection                             | 20  |

| 3.2.2.12    | Far-End Fault                                 | 20  |

| 3.2.3       | 100Base-TX Transceiver                        |     |

| 3.2.3.1     | Transmit Drivers                              |     |

| 3.2.3.2     | Twisted-Pair Receiver                         |     |

| 3.2.4       | 10Base-T Module                               |     |

| 3.2.4.1     | Operation Modes                               |     |

| 3.2.4.2     | Manchester Encoder/Decoder                    |     |

| 3.2.4.3     | Transmit Driver and Receiver                  |     |

| 3.2.4.4     | Smart Squelch                                 |     |

| 3.2.5       | Carrier Sense                                 |     |

| 3.2.6       | Jabber Function                               |     |

| 3.2.7       | Link Test Function                            |     |

| 3.2.8       | Automatic Link Polarity Detection             |     |

| 3.2.9       | Clock Synthesizer                             |     |

| 3.2.10      | Auto Negotiation                              |     |

| 3.3         | Memory Block Description                      |     |

| 3.4         | Switch Functional Description                 |     |

| 3.4.1       | Basic Operation                               |     |

| 3.4.1.1     | Address Learning                              |     |

| 3.4.1.2     | Address Recognition and Packet Forwarding     | 23  |

## ADM6999G/GX

## **Table of Contents**

| 3.4.1.3 | Address Aging                             |    |

|---------|-------------------------------------------|----|

| 3.4.1.4 | Back off Algorithm                        |    |

| 3.4.1.5 | Inter-Packet Gap (IPG)                    |    |

| 3.4.1.6 | Illegal Frames                            |    |

| 3.4.1.7 | Half Duplex Flow Control                  | 24 |

| 3.4.1.8 | Full Duplex Flow Control                  |    |

| 3.4.1.9 | Broadcast Storm Filter                    |    |

| 3.4.2   | Auto TP MDIX Function                     |    |

| 3.4.3   | Port Locking                              |    |

| 3.4.4   | VLAN Setting & Tag/Untag & Port-base VLAN |    |

| 3.4.5   | Priority Setting                          |    |

| 3.4.6   | LED Display                               |    |

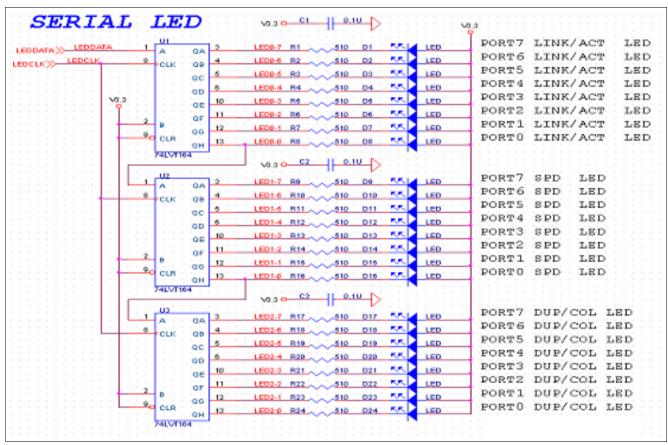

| 3.4.6.1 | Serial LED Interface                      |    |

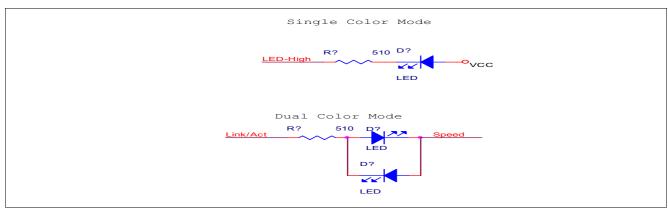

| 3.4.6.2 | LED Display Mode                          |    |

| 3.5     | EEPROM Content                            | 29 |

| 3.5.1   | EEPROM Registers Overview                 | 31 |

| 3.5.1.1 | EEPROM Registers Description              | 33 |

| 3.6     | EEPROM Access Description                 | 61 |

| 4       | Serial Management                         | 63 |

| 4.1     | Serial Registers Map                      |    |

| 4.1.1   | Serial Registers Description              |    |

| 4.2     | Serial Interface Timing                   |    |

| -       | · · · · · · · · · · · · · · · · · · ·     |    |

| 5       | ADM6999GTX/FX Interface                   |    |

| 5.1     | TP Interface                              |    |

| 5.2     | FX Interface                              | 78 |

| 6       | DC Characteristics                        | 80 |

| 7       | AC Characteristics                        | 81 |

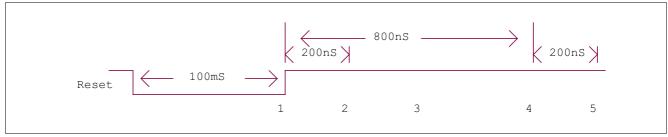

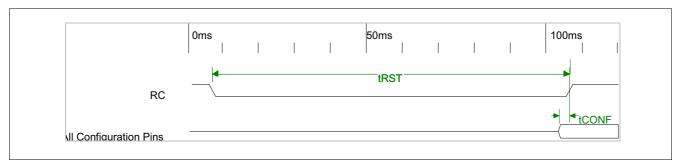

| 7.1     | Power On Reset                            | 81 |

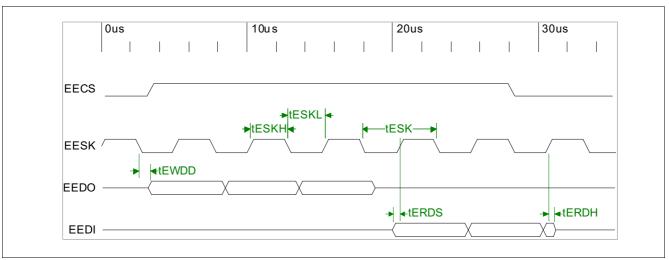

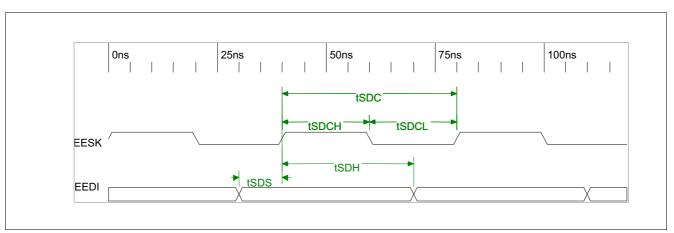

| 7.2     | EEPROM Data Timing                        |    |

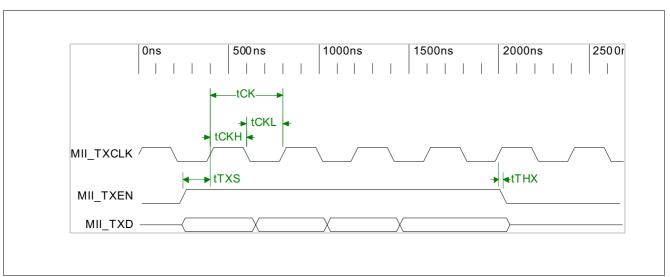

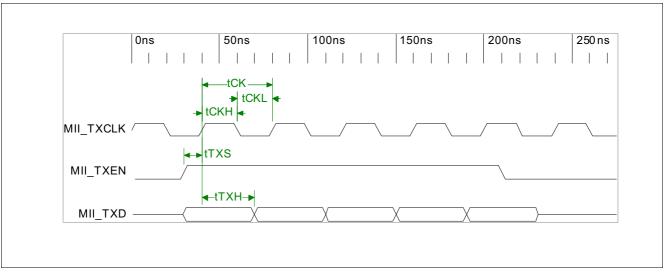

| 7.3     | 10Base-TX MII Input Timing                |    |

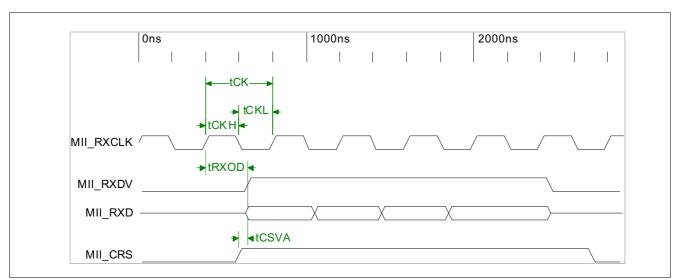

| 7.4     | 10Base-TX MII Output Timing               |    |

| 7.5     | 100Base-TX MII Input Timing               |    |

| 7.6     | 100Base-TX MII Output Timing              |    |

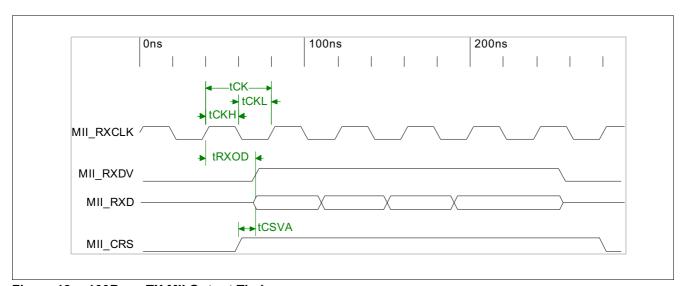

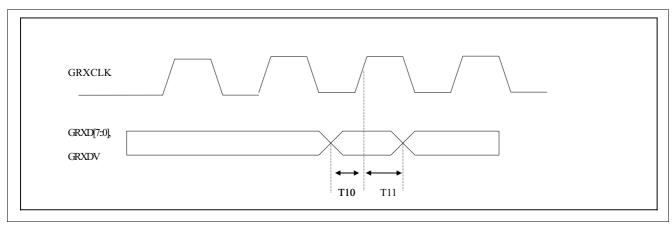

| 7.7     | GMII Receive Signals Timing               |    |

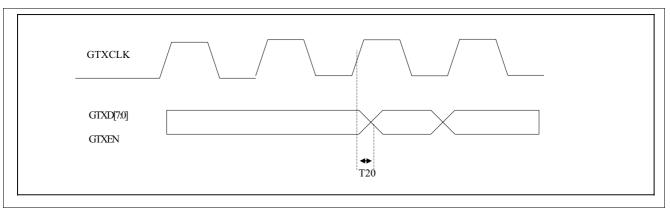

| 7.8     | GMII Transmit Signals Timing              |    |

| 7.9     | SMI Timing                                |    |

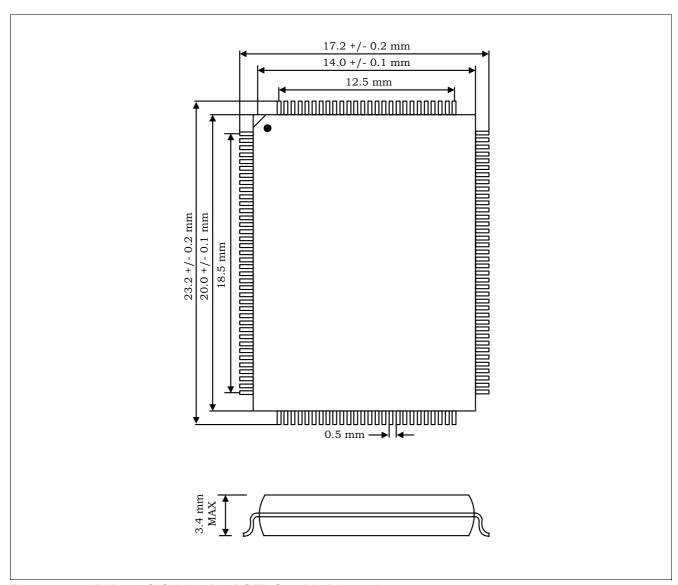

| R       | Package                                   |    |

| D       | Package                                   | ი/ |

**List of Figures**

## **List of Figures**

| Figure 1  | 8 TP/FX PORT + 1 GMII PORT 128 Pin Diagram 10                      |

|-----------|--------------------------------------------------------------------|

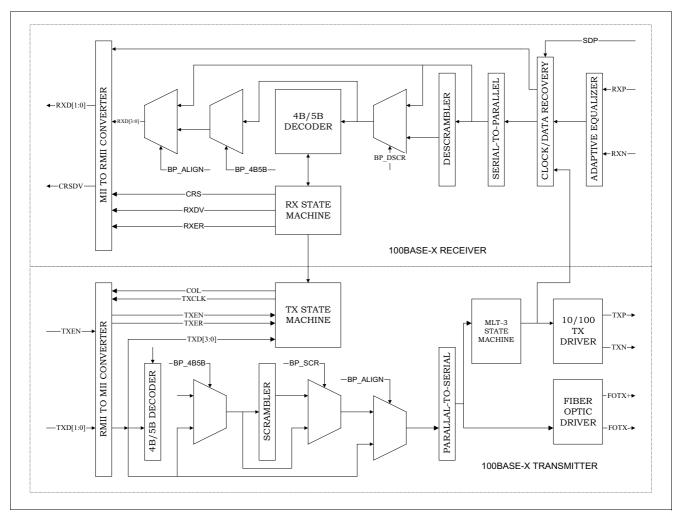

| Figure 2  | 100Base-X Module 18                                                |

| Figure 3  | Serial LED Interface 27                                            |

| Figure 4  | LED Display Mode 28                                                |

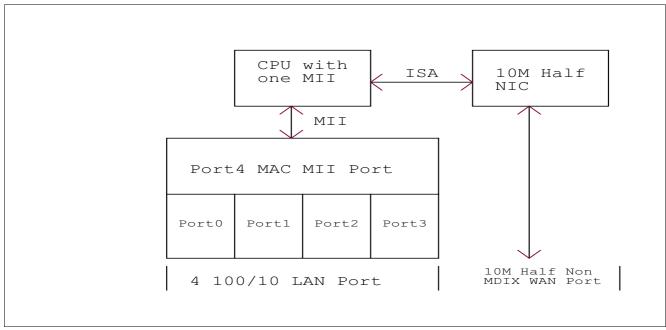

| Figure 5  | Router old architecture 46                                         |

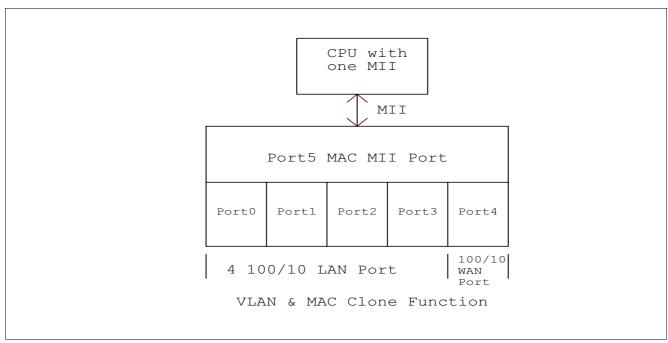

| Figure 6  | New architecture by using ADM6999G/GX serial chip VLAN function 47 |

| Figure 7  | ADM6999G/GX serial chips EEPROM pins operation 61                  |

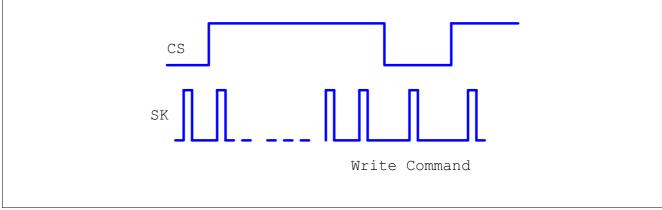

| Figure 8  | EEPROM Writing Command 62                                          |

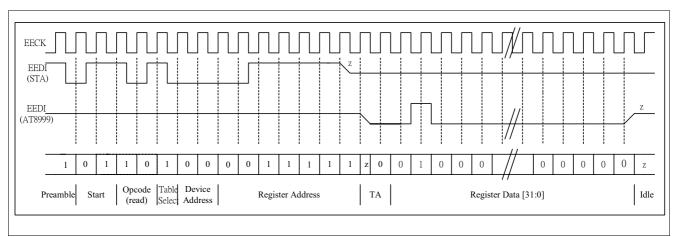

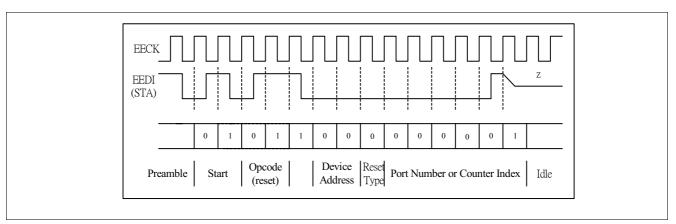

| Figure 9  | Serial Interface Timing X 76                                       |

| Figure 10 | Serial Interface Timing Y 77                                       |

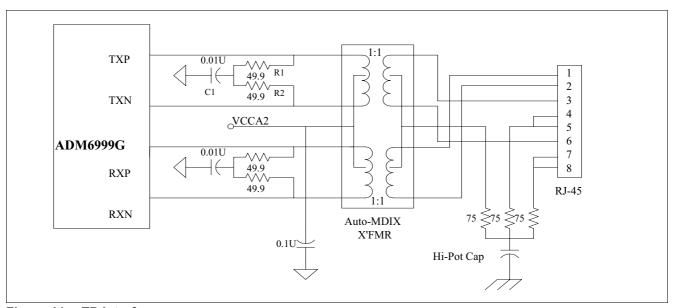

| Figure 11 | TP Interface 78                                                    |

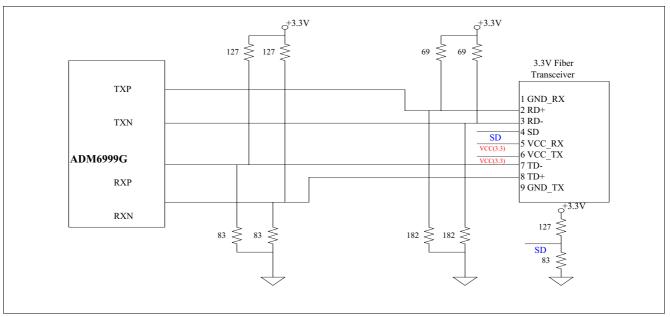

| Figure 12 | FX Interface 79                                                    |

| Figure 13 | Power On Reset 81                                                  |

| Figure 14 | EEPROM Data Timing 81                                              |

| Figure 15 | 10Base-TX MII Input Timing 82                                      |

| Figure 16 | 10Base-TX MII Output Timing 83                                     |

| Figure 17 | 100Base-TX MII Input Timing 84                                     |

| Figure 18 | 100Base-TX MII Output Timing 84                                    |

| Figure 19 | GMII Receive Signals Timing 85                                     |

| Figure 20 | GMII Transmit Signals Timing 86                                    |

| Figure 21 | SMI Timing 86                                                      |

| Figure 22 | ADM6999G/GX 128 Pin PQFP Outside Dimension 87                      |

**List of Tables**

## **List of Tables**

| Table 1  | Abbreviations for Pin Type 11                        |

|----------|------------------------------------------------------|

| Table 2  | Abbreviations for Buffer Type 11                     |

| Table 3  | ADM6999G/GX-128 PINS(8 TP + GPSI/RMII) 12            |

| Table 4  | Port Rising/Falling Threshold 25                     |

| Table 5  | LED Display 27                                       |

| Table 6  | EEPROM Map 29                                        |

| Table 7  | Registers Address SpaceRegisters Address Space 31    |

| Table 8  | Registers Overview 31                                |

| Table 9  | Register Access Types 32                             |

| Table 10 | Registers Clock Domains Registers Clock Domains 33   |

| Table 11 | PCR_x Registers Table 35                             |

| Table 12 | Per Port Rising Threshold 44                         |

| Table 13 | Per Port Falling Threshold 44                        |

| Table 14 | Drop Scheme for each Queue 44                        |

| Table 15 | ADM6996 Port Mapping with ADM6999G/GX 45             |

| Table 16 | VLAN_MTR_x Registers Table 51                        |

| Table 17 | RC & EEPROM Content Relationship 61                  |

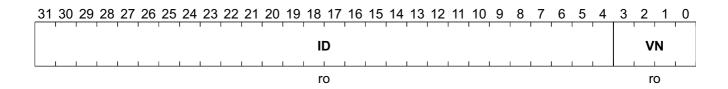

| Table 18 | Registers Address SpaceRegisters Address Space 63    |

| Table 19 | Registers Overview 63                                |

| Table 20 | Register Access Types 64                             |

| Table 21 | Registers Clock Domains Registers Clock Domains 65   |

| Table 22 | Port Registers RPC_x 71                              |

| Table 23 | Absolute Maximum Ratings 80                          |

| Table 24 | Recommended Operating Conditions 80                  |

| Table 25 | DC Electrical Characteristics for 3.3 V Operation 80 |

| Table 26 | Power On Reset 81                                    |

| Table 27 | EEPROM Data Timing 82                                |

| Table 28 | 10Base-TX MII Input Timing 82                        |

| Table 29 | 10Base-TX MII Output Timing 83                       |

| Table 30 | 100Base-TX MII Input Timing 84                       |

| Table 31 | 100Base-TX MII Output Timing 85                      |

| Table 32 | GMII Receive Signals Timing 85                       |

| Table 33 | GMII Transmit Signals Timing 86                      |

| Table 34 | SMI Timing 86                                        |

Introduction

## 1 Introduction

## 1.1 General Description

The ADM6999G/GX is a high performance, low cost, and highly integration (Controller, PHY and Memory) eight-port 10/100 Mbps TX/FX plus one 10/100/1000 GMII port Ethernet switch controller with all ports supporting 10/100 Mbps Full/Half duplex and Gigabit port support Full Duplex switch function. The ADM6999G/GX is intended for applications to stand alone the bridge for low cost SOHO market such as 8+1G. The ADM6999GX is the environmentally friendly "green" package version.

ADM6999G/GX provides most advanced functions such as: 802.1p (Q.O.S.), 802.1q (VLAN), Port MAC Address Locking, Management, Port Status, TP Auto-MDIX, 25M Crystal & Extra ninth Port (GMII) functions to meet the customer's requests on Switch demand.

The built-in 768K SRAM used for the packet buffer and address learning table is divided into 512 bytes/block to achieve the optimized memory utilization through complicated link list on packets with various lengths.

ADM6999G/GX also supports priority features by Port-Base, VLAN and IP TOS field checking. Users can easily set a different priority mode in individual port, through a small low-cost micro controller to initialize or on-the-fly to configure. Each output port supports two queues in the way of fixed N: 1 fairness queuing to fit the bandwidth demand on various types of packet such as Voice, Video and data. 802.1Q, Tag/Untag, and up to 32 groups of VLAN are also supported. ADM6999G/GX learns user to define 4 or 5 bits of VLAN ID.

An intelligent address recognition algorithm makes ADM6999G/GX to recognize up to 2048 different MAC addresses and enables filtering and forwarding at full wire speed.

Port MAC address Locking function is also supported by ADM6999G/GX to use on Building Internet access to prevent multiple users share one port traffic.

## 1.2 Features

Main features:

- Supports eight 10M/100M auto-detect Half/Full duplex switch ports with TX/FX interfaces and one GMII/MII port.

- Built-in 12Kx64 SRAM

- · Supports 2048 MAC addresses table

- Supports two queue for Qos

- Supports priority features by Port-Based, 802.1p VLAN & IP TOS of packets

- Supports Store & Forward architecture and performs forwarding and filtering at non-blocking full wire speed

- Supports buffer allocation with 512 bytes per block

- Supports Aging function Enable/Disable

- Supports serial Single/Dual color mode with Power On auto diagnostic.

- Supports 802.3x Flow Control pause packet for Full Duplex in case buffer is full

- Supports Back Pressure function for Half Duplex operation in case buffer is full

- Supports packet length up to 1522 bytes

- Broadcast Storming Filter function

- Supports 802.1Q VLAN. Up to 16/32 VLAN groups are implemented by the user to define four/five bits of VLAN.

- · Supports MAC-clone feature

- Supports TP interface **Auto MDIX** function for auto TX/RX swap by strapping-pin

- Easy Management 32bits smart counter for per port RX/TX byte/packet count, error count and collision count

- Supports PHY status output for management system

- 25M Crystal only for the whole system. Output 10M/25M/50M for different interface

- 128 QFP package with 0.18um technology. 1.8 V/3.3 V power supply

Introduction

## 1.3 Applications

ADM6999G/GX in 128-pin PQFP:

- Standalone SOHO 8+1 Gigabit Switch as start-kit

- Gigabit up link module, etc..

## 2 Input and Output Signals

This chapter describes Pin Diagram and Pin Descriptions.

## 2.1 Pin Diagram

Figure 1 8 TP/FX PORT + 1 GMII PORT 128 Pin Diagram

## 2.2 Pin Type and Buffer Type Abbreviations

Standardized abbreviations:

Table 1 Abbreviations for Pin Type

| Abbreviations | Description                                 |  |  |  |  |  |  |

|---------------|---------------------------------------------|--|--|--|--|--|--|

| I             | Standard input-only pin. Digital levels.    |  |  |  |  |  |  |

| 0             | Output. Digital levels.                     |  |  |  |  |  |  |

| I/O           | I/O is a bidirectional input/output signal. |  |  |  |  |  |  |

| Al            | Input. Analog levels.                       |  |  |  |  |  |  |

| AO            | Output. Analog levels.                      |  |  |  |  |  |  |

| AI/O          | Input or Output. Analog levels.             |  |  |  |  |  |  |

| PWR           | Power                                       |  |  |  |  |  |  |

| GND           | Ground                                      |  |  |  |  |  |  |

| MCL           | Must be connected to Low (JEDEC Standard)   |  |  |  |  |  |  |

| MCH           | Must be connected to High (JEDEC Standard)  |  |  |  |  |  |  |

| NU            | Not Usable (JEDEC Standard)                 |  |  |  |  |  |  |

| NC            | Not Connected (JEDEC Standard)              |  |  |  |  |  |  |

## Table 2 Abbreviations for Buffer Type

| Abbreviations | Description                                                                                                                                                                                                                                                                        |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Z             | High impedance                                                                                                                                                                                                                                                                     |

| PU1           | Pull up, 10 kΩ                                                                                                                                                                                                                                                                     |

| PD1           | Pull down, 10 kΩ                                                                                                                                                                                                                                                                   |

| PD2           | Pull down, 20 kΩ                                                                                                                                                                                                                                                                   |

| TS            | Tristate capability: The corresponding pin has 3 operational states: Low, high and high-impedance.                                                                                                                                                                                 |

| OD            | Open Drain. The corresponding pin has 2 operational states, active low and tristate, and allows multiple devices to share as a wire-OR. An external pull-up is required to sustain the inactive state until another agent drives it, and must be provided by the central resource. |

| OC            | Open Collector                                                                                                                                                                                                                                                                     |

| PP            | Push-Pull. The corresponding pin has 2 operational states: Active-low and active-high (identical to output with no type attribute).                                                                                                                                                |

| OD/PP         | Open-Drain or Push-Pull. The corresponding pin can be configured either as an output with the OD attribute or as an output with the PP attribute.                                                                                                                                  |

| ST            | Schmitt-Trigger characteristics                                                                                                                                                                                                                                                    |

| TTL           | TTL characteristics                                                                                                                                                                                                                                                                |

Data Sheet 11 Rev 1.31, 2005-11-25

## 2.3 Pin Descriptions

Table 3 ADM6999G/GX-128 PINS(8 TP + GPSI/RMII)<sup>1)2)</sup>

| Pin or Ball  | Name            | Pin  | Buffer | Function                              |

|--------------|-----------------|------|--------|---------------------------------------|

| No.          |                 | Туре | Type   |                                       |

| Twisted Pai  | ir Interface    |      |        |                                       |

| 126          | RXP0            | AI/O |        | Twisted Pair Receive Input Positive   |

| 2            | RXP1            |      |        |                                       |

| 11           | RXP2            |      |        |                                       |

| 15           | RXP3            |      |        |                                       |

| 24           | RXP4            |      |        |                                       |

| 28           | RXP5            |      |        |                                       |

| 37           | RXP6            |      |        |                                       |

| 41           | RXP7            |      |        |                                       |

| 127          | RXN0            | AI/O |        | Twisted Pair Receive Input Negative   |

| 1            | RXN1            |      |        |                                       |

| 12           | RXN2            |      |        |                                       |

| 14           | RXN3            |      |        |                                       |

| 25           | RXN4            |      |        |                                       |

| 27           | RXN5            |      |        |                                       |

| 38           | RXN6            |      |        |                                       |

| 40           | RXN7            |      |        |                                       |

| 123          | TXP0            | AI/O |        | Twisted Pair Transmit Output Positive |

| 5            | TXP1            |      |        |                                       |

| 8            | TXP2            |      |        |                                       |

| 18           | TXP3            |      |        |                                       |

| 21           | TXP4            |      |        |                                       |

| 31           | TXP5            |      |        |                                       |

| 34           | TXP6            |      |        |                                       |

| 44           | TXP7            |      |        |                                       |

| 124          | TXN0            | AI/O |        | Twisted Pair Transmit Output Negative |

| 4            | TXN1            |      |        |                                       |

| 9            | TXN2            |      |        |                                       |

| 17           | TXN3            |      |        |                                       |

| 22           | TXN4            |      |        |                                       |

| 30           | TXN5            |      |        |                                       |

| 35           | TXN6            |      |        |                                       |

| 43           | TXN7            |      |        |                                       |

| Ninth Port ( | GMII) Interface | es   |        | 1                                     |

Table 3 ADM6999G/GX-128 PINS(8 TP + GPSI/RMII)<sup>1)2)</sup> (cont'd)

| Pin or Ball<br>No. | Name   | Pin<br>Type | Buffer<br>Type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------|--------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 63                 | GTXD0  | I/O         | 8mA, PU        | Giga Port transmit data 0 Acts as GMII transmit data TXD0 synchronous to the rising edge of TXCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                    | GFCEN  | I/O         | 8mA, PU        | Setting GFCEN: Global Flow Control Enable.  At power-on-reset, latched as Flow control setting  0 <sub>B</sub> , Disable flow-control  1 <sub>B</sub> , Enable flow-control (default)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 61                 | GTXD1  | 0           | 8mA            | Giga Port Transmit Data bit 1~7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 60                 | GTXD2  |             |                | Synchronous to the rising edge of GTXCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 59                 | GTXD3  |             |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 55                 | GTXD4  |             |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 54                 | GTXD5  |             |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 51                 | GTXD6  |             |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 50                 | GTXD7  |             |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 62                 | P7FX   | I/O         | 8mA, PD        | Setting Port7 FX/TX Mode select Internal pull down.  0 <sub>B</sub> , Port7 as TX port  1 <sub>B</sub> , Port7 as FX port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                    | GTXER  | I/O         | 8mA, PD        | Giga Port Transmit Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 66                 | PHYAS0 | I/O         | 8mA, PD        | Setting PHYAS0: Chip physical address0 for multiple chip application on EEPROM access. Internal pull down Power on reset value PHYAS0 combines with PHYAS1(LEDDATA). PHYAD Gigabit PHY Address 00 08 <sub>H</sub> Master Master: ADM6999G/GX will read 93C46 EEPROM first Bank.(00 <sub>H</sub> ~27 <sub>H</sub> ). If there is no EEPROM then user must use 93C66 timing to write chip's register. If user put 93C46 with correct Signature then user writes chip register by 93C46 timing. If user put 93C66 then data put in Bank0. User can write chip register by 93C66 timing. User must assert one SK cycle when CS is at idle stage and chip internal registers are being writing. |

|                    | GTXEN  | I/O         | 8mA, PD        | Giga Port Transmit Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Table 3 ADM6999G/GX-128 PINS(8 TP + GPSI/RMII)<sup>1)2)</sup> (cont'd)

| Pin or Ball<br>No. | Name           | Pin<br>Type | Buffer<br>Type | Function                                                                                                                                                                                                        |

|--------------------|----------------|-------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 74                 | GRXD0          | I           | PD             | Giga Port receive data 0~7                                                                                                                                                                                      |

| 100                | GRXD1          |             |                | Synchronous to the rising edge of RXCLK                                                                                                                                                                         |

| 101                | GRXD2          |             |                |                                                                                                                                                                                                                 |

| 102                | GRXD3          |             |                |                                                                                                                                                                                                                 |

| 103                | GRXD4          |             |                |                                                                                                                                                                                                                 |

| 106                | GRXD5          |             |                |                                                                                                                                                                                                                 |

| 107                | GRXD6          |             |                |                                                                                                                                                                                                                 |

| 108                | GRXD7          |             |                |                                                                                                                                                                                                                 |

| 73                 | GRXDV          | I           | PD             | Giga Port receive data valid Internal pull down                                                                                                                                                                 |

| 68                 | GND            | I           | PD             | GND or NC at normal application                                                                                                                                                                                 |

| 78                 | GCOL           | I           | PD             | MII Port Collision input<br>Internal pull down                                                                                                                                                                  |

| 77                 | GCRS           | I           | PD             | Giga Port Carrier Sense<br>Internal pull down                                                                                                                                                                   |

| 58                 | GTXCLK         | 0           | 16mA           | Gigabit Port 125 MHz clock Output                                                                                                                                                                               |

| 72                 | GRXCLK         | I           |                | Giga Port Receive Clock Input                                                                                                                                                                                   |

| 67                 | TXCP8          | I           |                | MII Port Transmit clock Input                                                                                                                                                                                   |

| LED Interfa        | ce             | •           |                |                                                                                                                                                                                                                 |

| 86                 | LEDDATA        |             |                | Serial LED Data                                                                                                                                                                                                 |

|                    | PHYAS1         |             |                | Setting PHYAS1: Chip physical address1 for multiple chip application on EEPROM access. Internal pull down. See pin 66.                                                                                          |

| 109                | LEDCLK         |             |                | Serial LED Clock                                                                                                                                                                                                |

|                    | ANEN           |             |                | Setting ANEN: On power-on-reset, latched as Auto Negotiation capability for all ports.  0 <sub>B</sub> , Disable Auto Negotiation  1 <sub>B</sub> , Enable Auto Negotiation (defaulted by pulled up internally) |

| EEPROM/M           | anagement Inte | rface       |                |                                                                                                                                                                                                                 |

| 84                 | EEDO           | I           | TTL, PU        | <b>EEPROM Data Output</b> Serial data input from EEPROM. This pin is internally pull-up.                                                                                                                        |

| 80                 | EECS           | 0           | 4mA, PD        | <b>EEPROM Chip Select</b> This pin is an active high chip enable for EEPROM. When RC is low, it will be Tristate. This pin is internally pull-down.                                                             |

Table 3 ADM6999G/GX-128 PINS(8 TP + GPSI/RMII)<sup>1)2)</sup> (cont'd)

| Pin or Ball<br>No. | Name    | Pin<br>Type | Buffer<br>Type | Function                                                                                                                                                                                                                                               |

|--------------------|---------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 81                 | EECK    | I/O         | 4mA, PD        | Serial Clock                                                                                                                                                                                                                                           |

|                    |         |             |                | This pin is clock source for EEPROM.                                                                                                                                                                                                                   |

|                    | XOVEN   | I/O         | 4mA, PD        | Setting XOVEN: This pin is internally pull-down.  On power-on-reset, latched as P7~0 Auto MDIX enable or not.  Suggests externally pull up to enable Auto MDIX for all ports.  O <sub>B</sub> , Disable MDIX (defaulted)  1 <sub>B</sub> , Enable MDIX |

| 79                 | EEDI    | 0           | 4mA, PD        | EEPROM Serial Data Input This pin is output for serial data transfer.                                                                                                                                                                                  |

|                    | LEDMODE | 0           | 4mA, PD        | Setting LEDMODE This pin is internally pull-down. On power-on-reset, latched as Dual Color mode or not.  0 <sub>B</sub> , Single Color LED 1 <sub>B</sub> , Dual Color LED                                                                             |

| 98                 | MDIO    | I/O         | 8mA            | Management Data This pin is in-out to PHY. When RC is low, this pin will be tri-state.                                                                                                                                                                 |

| 97                 | MDC     | 0           | 8mA            | Management Data Clock This pin output 1 MHz clock to drive PHY and access corresponding speed and duplex data through MDIO.                                                                                                                            |

| Misc.              |         |             | <u> </u>       |                                                                                                                                                                                                                                                        |

| 85                 | CKO25M  | 0           | 8mA            | 25M Clock Output For GMII port                                                                                                                                                                                                                         |

| 117                | Control | 0           |                | FET Control Signal The pin is used to control FET for 3.3 V to 1.8 V regulator. Add 0.01 μf capacitor to GND.                                                                                                                                          |

| 120                | RTX     | А           |                | TX Resistor Add 1.1K %1(A1), 1K %1 (A2) resister to GND.                                                                                                                                                                                               |

| 118                | VREF    | Α           |                | Analog Reference Voltage                                                                                                                                                                                                                               |

| 112                | RC      | I           | ST             | RC Input for Power On reset Reset input pin                                                                                                                                                                                                            |

| 113                | XI      | Al          |                | <b>25M Crystal Input</b> 25M Crystal Input. Variation is limited to +/- 50ppm.                                                                                                                                                                         |

| 114                | ХО      | AO          |                | 25M Crystal Output When connected to oscillator, this pin should be left unconnected.                                                                                                                                                                  |

| 49                 | TEST    | I           | TTL            | TEST Value At normal application connects to GND.                                                                                                                                                                                                      |

| Chip Config        | uration |             |                |                                                                                                                                                                                                                                                        |

| 89                 | CFG0    | I           | TTL, PU        | Must Connected to GND                                                                                                                                                                                                                                  |

| 46                 | ALERT   | 0           |                | Alert LED Display This pin will show the status of power-on-diagnostic and broadcast traffic.                                                                                                                                                          |

Table 3 ADM6999G/GX-128 PINS(8 TP + GPSI/RMII)<sup>1)2)</sup> (cont'd)

| Pin or Ball                          | Name    | Pin  | Buffer | Function                                                                                                       |

|--------------------------------------|---------|------|--------|----------------------------------------------------------------------------------------------------------------|

| No.                                  |         | Type | Type   |                                                                                                                |

| Power/Grou                           | nd      |      |        |                                                                                                                |

| 3, 10, 16, 23,<br>29, 36, 42,<br>125 | GNDA    | I    |        | Ground Used by AD Block                                                                                        |

| 6, 7, 19, 20,<br>32, 33, 45,<br>122  | VCCA2   | I    |        | 1.8 V, Power Used by TX Line Driver                                                                            |

| 13, 26, 39,<br>128                   | VCCAD   | I    |        | 3.3 V, Power Used by AD Block                                                                                  |

| 119                                  | GNDBIAS | I    |        | Ground Used by Bias Block                                                                                      |

| 121                                  | VCCBIAS | I    |        | 3.3 V, Power Used by Bias Block                                                                                |

| 116                                  | GNDPLL  | I    |        | Ground used by PLL                                                                                             |

| 115                                  | VCCPLL  | I    |        | 1.8 V, Power used by PLL                                                                                       |

| 47, 52, 64,<br>76, 83, 93,<br>111    | GNDIK   | I    |        | Ground Used by Digital Core                                                                                    |

| 48, 53, 65,<br>75, 82, 94,<br>110    | VCCIK   | I    |        | 1.8 V, Power Used by Digital Core                                                                              |

| 57, 70, 87,<br>99, 104               | GNDO    | I    |        | Ground Used by Digital Pad                                                                                     |

| 56, 71, 88,<br>105                   | VCC3O   | 1    |        | 3.3 V, Power Used by Digital Pad                                                                               |

| 69                                   | GND     | I    | TTL    | Scan Enable This pin will be used as the scan enable input for testing. Connects to GND at normal application. |

| NC pins                              |         | •    | •      |                                                                                                                |

| 90, 91, 92,<br>95, 96                | NC      |      |        | No Connect                                                                                                     |

<sup>1)</sup> Do not swap TP port +- signal. It may cause link fail when link partner does not support Auto Polarity function.

<sup>2)</sup> I: Input, O: Output, I/O: Bi-directional, OD: Open drain, SCHE: Schmitt-Trigger, PD: internal pull-down, PU: internal pull-up

## 3 Descriptions

This chapter provides Functional Description, 10/100M PHY Block Description, Memory Block Description, Switch Functional Description, EEPROM Content and EEPROM Access Description.

## 3.1 Functional Description

The ADM6999G/GX integrates eight 100Base-X physical sub-layer (PHY), 100Base-TX physical medium dependent (PMD) transceivers, eight complete 10Base-T modules, 8 port 100/10 switch controller, and one 10/100/1000 MAC and memory into a single chip for both 10Mbits/s, 100Mbits/s, 1000Mbits/s Ethernet switch operations. It also supports 100Base-FX operation through external fiber-optic transceivers. The device is capable of operating in either Full Duplex mode, Half-Duplex mode in 10Mbits/s and 100Mbits/s, or Full duplex only at 1000Mbits/s operation. Operational modes can be selected by hardware configuration pins, software settings of management registers, or determined by the on-chip auto negotiation logic.

The ADM6999G/GX consists of three major blocks:

- 10/100M PHY Block

- Switch Controller Block

- Built-in 12Kx64 SSRAM

## 3.2 10/100M PHY Block Description

The 100Base-X section of the device implements the following functional blocks:

- 100Base-X physical coding sub-layer (PCS)

- 100Base-X physical medium attachment (PMA)

- Twisted-pair transceiver (PMD)

The 100Base-X and 10Base-T sections share the following functional blocks:

- · Clock synthesizer module

- MII Registers

- IEEE 802.3u auto negotiation

#### 3.2.1 100Base-X Module

The ADM6999G/GX implements 100Base-X compliant PCS, PMA and 100Base-TX compliant TP-PMD as illustrated in **Figure 2**. Bypass options for each of the major functional blocks within the 100Base-X PCS provide flexibility for various applications. 100Mbits/s PHY loop back is included for the diagnostic purpose.

#### 3.2.2 100Base-X Receiver

The 100Base-X receiver consists of functional blocks required to recover and condition the 125Mbits/s received data stream. The ADM6999G/GX implements the 100Base-X received state machine diagram as given in ANSI/IEEE Standard 802.3u, Clause 24. The 125Mbits/s received data stream may originate from the on-chip twisted-pair transceiver in a 100Base-TX application. Alternatively, the received data stream may be generated by an external optical receiver as in a 100Base-FX application.

The receiver block consists of the following functional sub-blocks:

- A/D Converter

- · Adaptive Equalizer and timing recovery module

- NRZI/NRZ and serial/parallel decoder

- De-scrambler

- Symbol alignment block

- Symbol Decoder

- · Collision Detect Block

- · Carrier sense Block

#### Stream decoder block

Figure 2 100Base-X Module

#### 3.2.2.1 A/D Converter

High performance A/D converter with 125 MHz sampling rate converts signals received on RXP/RXN pins to 6 bits data streams; besides it possess auto-gain-control capability that will further improve receiving performance especially under long cable or harsh detrimental signal integrity. Due to high pass characteristic on transformer, built in base-line-wander correcting circuit will cancel it out and restore its DC level.

## 3.2.2.2 Adaptive Equalizer and Timing Recovery Module

All digital design is especial immune from noise environments and achieves better correlation between production and system testing. Baud rate Adaptive Equalizer/Timing Recovery compensates line loss induced from twisted pair and tracks far end clock at 125M samples per second. Adaptive Equalizer implemented with Feed forward and Decision Feedback techniques meet the requirement of BER less than 10-12 for transmission on CAT5 twisted pair cable ranging from 0 to 120 meters.

#### 3.2.2.3 NRZI/NRZ and Serial/Parallel Decoder

The recovered data is converted from NRZI to NRZ. The data is not necessarily aligned to 4B/5B code group's boundary.

## 3.2.2.4 Data De-scrambling

The de-scrambler acquires synchronization with the data stream by recognizing idle bursts of 40 or more bits and locking its deciphering Linear Feedback Shift Register (LFSR) to the state of the scrambling LFSR. Upon achieving synchronization, the incoming data is XORed by the deciphering LFSR and de-scrambled.

In order to maintain synchronization, the de-scrambler continuously monitors the validity of the unscrambled data that it generates. To ensure this, a link state monitor and a hold timer are used to constantly monitor the synchronization status. Upon synchronization of the de-scrambler the hold timer starts a 722 us countdown. Upon detection of sufficient idle symbols within the 722 us period, the hold timer will reset and begin a new countdown. This monitoring operation will continue indefinitely given a properly operating network connection with good signal integrity. If the link state monitor does not recognize sufficient unscrambled idle symbols within 722 us period, the de-scrambler will be forced out of the current state of synchronization and reset in order to re-acquire synchronization.

## 3.2.2.5 Symbol Alignment

The symbol alignment circuit in the ADM6999G/GX determines code word alignment by recognizing the /J/K delimiter pair. This circuit operates on unaligned data from the de-scrambler. Once the /J/K symbol pair (11000 10001) is detected, subsequent data is aligned on a fixed boundary.

## 3.2.2.6 Symbol Decoding

The symbol decoder functions as a look-up table that translates incoming 5B symbols into 4B nibbles. The symbol decoder first detects the /J/K symbol pair preceded by idle symbols and replaces the symbol with MAC preamble. All subsequent 5B symbols are converted to the corresponding 4B nibbles for the duration of the entire packet. This conversion ceases upon the detection of the /T/R symbol pair denoting the end of stream delimiter (ESD). The translated data presented on the internal RXD[3:0] signal lines with RXD[0] represents the least significant bit of the translated nibble.

## 3.2.2.7 Valid Data Signal

The valid data signal (RXDV) indicates that recovered and decoded nibbles are being presented on the internal RXD[3:0] synchronous to receive clock, RXCLK. RXDV is asserted when the first nibble of translated /J/K is ready for transfer over the internal MII. It remains active until either the /T/R delimiter is recognized, link test indicates failure, or no signal is detected. On any of these conditions, RXDV is de-asserted.

#### 3.2.2.8 Receive Errors

The RXER signal is used to communicate receiver error conditions. While the receiver is in a state of holding RXDV asserted, the RXER will be asserted for each code word that does not map to a valid code-group.

#### 3.2.2.9 100Base-X Link Monitor

The 100Base-X link monitor function allows the receiver to ensure that reliable data is being received. Without reliable data reception, the link monitor will halt both transmitting and receiving operations until such time that a valid link is detected.

The ADM6999G/GX performs the link integrity test as outlined in IEEE 100Base-X (Clause 24) link monitor state diagram. The link status is multiplexed with 10Mbits/s link status to form the reportable link status bit in serial management register 1<sub>H</sub>, and driven to the LNKACT pin.

When persistent signal energy is detected on the network, the logic moves into a Link-Ready state after approximately 500  $\mu$ s, and waits for an enable from the auto negotiation module. When receiving, the link-up state is entered, and the transmission and reception logic blocks become active. Should auto negotiation be disabled, the link integrity logic moves immediately to the link-up state after entering the link-ready state.

Data Sheet 19 Rev 1.31, 2005-11-25

#### 3.2.2.10 Carrier Sense

Carrier sense (CRS) for 100Mbits/s operation is asserted upon the detection of two noncontiguous zeros occurring within any 10-bit boundary of the received data stream.

The carrier sense function is independent of symbol alignment. In switch mode, CRS is asserted during either packet transmission or reception. For repeater mode, CRS is asserted only during packet reception. When the idle symbol pair is detected in the received data stream, CRS is de-asserted. In repeater mode, CRS is only asserted due to receive activity. CRS is intended to encapsulate RXDV.

#### 3.2.2.11 Bad SSD Detection

A bad start of stream delimiter (Bad SSD) is an error condition that occurs in the 100Base-X receiver if carrier is detected (CRS asserted) and a valid /J/K set of code-group (SSD) is not received.

If this condition is detected, then the ADM6999G/GX will assert RXER and present RXD[3:0] = 1110 to the internal MII for the cycles corresponding to the received 5B code-groups until at least two idle code-groups are detected. Once at least two idle code groups are detected, RXER and CRS become de-asserted.

#### 3.2.2.12 Far-End Fault

Auto negotiation provides a mechanism for transferring information from the Local Station to the link Partner that a remote fault has occurred for 100Base-TX. As auto negotiation is not currently specified for the operation over fiber, the far end fault indication function (FEFI) provides this capability for 100Base-FX applications.

A remote fault is an error in the link that one station can detect while the other cannot. An example of this is a disconnected wire at a station's transmitter. This station will be receiving valid data and detect that the link is good via the link integrity monitor, but will not be able to detect that its transmission is not propagating to the other station.

A 100Base-FX station that detects such a remote fault may modify its transmitted idle stream from all ones to a group of 84 ones followed by a single 0. This is referred to as the FEFI idle pattern.

#### 3.2.3 100Base-TX Transceiver

ADM6999G/GX implements a TP-PMD compliant transceiver for 100Base-TX operation. The differential transmitting driver is shared by the 10Base-T and 100Base-TX subsystems. This arrangement results in one device that uses the same external magnetic for both the 10Base-T and the 100Base-TX transmissions with simple RC component connections. The individually wave-shaped 10Base-T and 100Base-TX transmitting signals are multiplexed in the transmission output driver selection.

#### 3.2.3.1 Transmit Drivers

The ADM6999G/GX 100Base-TX transmission driver implements MLT-3 translation and wave-shaping functions. The rise/fall time of the output signal is closely controlled to conform to the target range specified in the ANSI TP-PMD standard.

#### 3.2.3.2 Twisted-Pair Receiver

For 100Base-TX operation, the incoming signal is detected by the on-chip twisted-pair receiver that consists of a differential line receiver, an adaptive equalizer and a base-line wander compensation circuits.

The ADM6999G/GX uses an adaptive equalizer that changes filter frequency response in accordance with cable length. The cable length is estimated based on the incoming signal strength. The equalizer tunes itself automatically for any cable length to compensate for the amplitude and phase distortions incurred from the cable.

Data Sheet 20 Rev 1.31, 2005-11-25

#### 3.2.4 10Base-T Module

The 10Base-T Transceiver Module is IEEE 802.3 compliant. It includes the receiver, transmitter, collision, heartbeat, loop back, jabber, wave shaper, and link integrity functions, as defined in the standard.

The ADM6999G/GX 10Base-T module is comprised of the following functional blocks:

- Manchester encoder and decoder

- · Collision detector

- · Link test function

- · Transmit driver and receiver

- · Serial and parallel interface

- Jabber and SQE test functions

- Polarity detection and correction

## 3.2.4.1 Operation Modes

The ADM6999G/GX 10Base-T module is capable of operating in either half-duplex mode or full-duplex mode. In half-duplex mode, the ADM6999G/GX functions as an IEEE 802.3 compliant transceiver with fully integrated filtering. The COL signal is asserted during collisions or jabber events, and the CRS signal is asserted during transmitting and receiving. In full duplex mode the ADM6999G/GX can simultaneously transmit and receive data.

#### 3.2.4.2 Manchester Encoder/Decoder

Data encoding and transmission begin when the transmission enable input (TXEN) goes high and continue as long as the transceiver is in good link state. Transmission ends when the transmission enable input goes low. The last transition occurs at the center of the bit cell if the last bit is a 1, or at the boundary of the bit cell if the last bit is 0. Decoding is accomplished by a differential input receiver circuit and a phase-locked loop that separate the Manchester-encoded data stream into clock signals and NRZ data. The decoder detects the end of a frame when no more mid bit transitions are detected. Within one and half bit times after the last bit, carrier sense is de-asserted.

#### 3.2.4.3 Transmit Driver and Receiver

The ADM6999G/GX integrates all the required signal conditioning functions in its 10Base-T block such that external filters are not required. Only one isolation transformer and impedance matching resistors are needed for the 10Base-T transmitting and receiving interface. The internal transmitting filter ensures that all the harmonics in the transmission signal are attenuated properly.

## 3.2.4.4 Smart Squelch

The smart squelch circuit is responsible for determining when valid data is present on the differential reception. The ADM6999G/GX implements an intelligent receiving squelch on the RXP/RXN differential inputs to ensure that impulse noise on the receiving inputs will not be mistaken for a valid signal. The squelch circuitry employs a combination of amplitude and timing measurements (as specified in the IEEE 802.3 10Base-T standard) to determine the validity of data on the twisted-pair inputs.

The signal at the start of the packet is checked by the analog squelch circuit and any pulses not exceeding the squelch level (either positive or negative, depending upon polarity) will be rejected. Once this first squelch level is overcome correctly, the opposite squelch level must then be exceeded within 150ns. Finally, the signal must exceed the original squelch level within an additional 150ns to ensure that the input waveform will not be rejected.

Only after all these conditions have been satisfied a control signal will be generated to indicate the remainder of the circuitry that valid data is present.

Valid data is considered to be present until the squelch level has not been generated for a time longer than 200 ns, indicating end of packet. Once good data has been detected, the squelch levels are reduced to minimize the effect

Data Sheet 21 Rev 1.31, 2005-11-25

of noise, causing premature end-of-packet detection. The receiving squelch threshold level can be lowered for use in longer cable applications. This is achieved by setting bit 10 of register address 11<sub>H</sub>.

#### 3.2.5 Carrier Sense

Carrier Sense (CRS) is asserted due to receive activity once valid data is detected via the smart squelch function. For 10 Mbits/s half duplex operation, CRS is asserted during either packet transmission or reception. For 10 Mbits/s full duplex and repeater mode operations, the CRS is asserted only due to receive activity.

#### 3.2.6 Jabber Function

The jabber function monitors the ADM6999G/GX output and disables the transmitter if it attempts to transmit a longer than legal sized packet. If TXEN is high for greater than 24ms, the 10Base-T transmitter will be disabled. Once disabled by the jabber function, the transmitter stays disabled for the entire time that the TXEN signal is asserted. This signal has to be de-asserted for approximately 256 ms (The un-jab time) before the jabber function re-enables the transmit outputs. The jabber function can be disabled by programming bit 4 of register address 10<sub>H</sub> to high.

#### 3.2.7 Link Test Function

A link pulse is used to check the integrity of the connection with the remote end. If valid link pulses are not received, the link detector disables the 10Base-T twisted-pair transmitter, receiver, and collision detection functions.

The link pulse generator produces pulses as defined in IEEE 802.3 10Base-T standard. Each link pulse is nominally 100ns in duration and is transmitted every 16 ms, in the absence of transmit data.

## 3.2.8 Automatic Link Polarity Detection

ADM6999G/GX's 10Base-T transceiver module incorporates an "automatic link polarity detection circuit". The inverted polarity is determined when seven consecutive link pulses of inverted polarity or three consecutive packets are received with inverted end-of-packet pulses. If the input polarity is reversed, the error condition will be automatically corrected and reported in bit 5 of register 10<sub>H</sub>.

## 3.2.9 Clock Synthesizer

The ADM6999G/GX implements a clock synthesizer that generates all the reference clocks needed from a single external frequency source. The clock source must be a TTL level signal at 25 MHz +/- 50ppm

#### 3.2.10 Auto Negotiation

The Auto Negotiation function provides a mechanism for exchanging configuration information between two ends of a link segment and automatically selecting the highest performance mode of operations supported by both devices. Fast Link Pulse (FLP) Bursts provide the signaling used to communicate auto negotiation abilities between two devices at each end of a link segment. For further details regarding auto negotiation, refer to Clause 28 of the IEEE 802.3u specification. The ADM6999G/GX supports four different Ethernet protocols, so the inclusion of auto negotiation ensures that the highest performance protocol will be selected based on the ability of the link partner.

Highest priority relative to the following list:

- 1. 100Base-TX full duplex (highest priority)

- 2. 100Base-TX half duplex

- 3. 10Base-T full duplex

- 4. 10Base-T half duplex (lowest priority)

Data Sheet 22 Rev 1.31, 2005-11-25

## 3.3 Memory Block Description

ADM6999G/GX builds in 768K bits memory inside. Memory buffer is divided in two blocks. One is MAC addressing table and another one is data buffer.

MAC address Learning Table size is 2048 entries with each entry occupying eight bytes length. These eight bytes data include 6 bytes source address, VLAN information, Port information and Aging counter.

Data buffer is divided into 512 bytes/block. ADM6999G/GX buffer management is fixed block number for each port and all port share one global buffer. This architecture can get better memory utilization and network balance on different speed and duplex test conditions.

Received packet will be separate in several 512 bytes/block and chain together. If the packet size is more than 512 bytes then ADM6999G/GX will chain two or more blocks to store receiving packet.

## 3.4 Switch Functional Description

The ADM6999G/GX uses a "store & forward" switching approach for the following reason:

Store & forward switches allow switching between different speed media (e.g. 10BaseX and 100BaseX). Such switches require the large elastic buffer especially bridging between a server on a 100Mbps network and clients on a 10Mbps segment.

Store & forward switches improve overall network performance by acting as a "network cache"

Store & forward switches prevent the forwarding of corrupted packets by the frame check sequence (FCS) before forwarding to the destination port.

## 3.4.1 Basic Operation

The ADM6999G/GX receives incoming packets from one of its ports, searches in the Address Table for the Destination MAC Address and then forwards the packet to the other port within the same VLAN group, if appropriate. If the destination address is not found in the address table, the ADM6999G/GX treats the packet as a broadcast packet and forwards the packet to the other ports within the same VLAN group.

The ADM6999G/GX automatically learns the port number of attached network devices by examining the Source MAC Address of all incoming packets at wire speed. If the Source Address is not found in the Address Table, the device adds it to the table.

## 3.4.1.1 Address Learning

The ADM6999G/GX uses a hash algorithm to learn the MAC address and can learn up to 2K MAC addresses. Address is stored in the Address Table. The ADM6999G/GX searches for the Source Address (SA) of an incoming packet in the Address Table and acts as below:

If the SA was not found in the Address Table (a new address), the ADM6999G/GX waits until the end of the packet (non-error packet) and updates the Address Table. If the SA was found in the Address Table, then aging value of each corresponding entry will be reset to 0.

When the DA is PAUSE command, the learning process will be disabled automatically by ADM6999G/GX.

## 3.4.1.2 Address Recognition and Packet Forwarding

The ADM6999G/GX forwards the incoming packets between bridged ports according to the Destination Address (DA) as below. All the packet forwarding will check VLAN first. A forwarding port must be within the same VLAN as the source port.

- 1. If the DA is an UNICAST address and the address was found in the Address Table, the ADM6999G/GX will check the port number and acts as follows:

- a) If the port number is equal to the port on which the packet was received, the packet is discarded.

- b) If the port number is different, the packet is forwarded across the bridge.

- 2. If the DA is an UNICAST address and the address was not found, the ADM6999G/GX treats it as a multicast packet and forwards across the bridge.

- 3. If the DA is a Multicast address, the packet is forwarded across the bridge.

- 4. If the DA is PAUSE Command (01-80-C2-00-00-01), then this packet will be dropped by ADM6999G/GX. ADM6999G/GX can issue and learn PAUSE command.

- 5. ADM6999G/GX will forward the packet with DA of (01-80-C2-00-00-00), filter out the packet with DA of (01-80-C2-00-00-01), and forward the packet with DA of (01-80-C2-00-00-02 ~ 01-80-C2-00-00-0F)

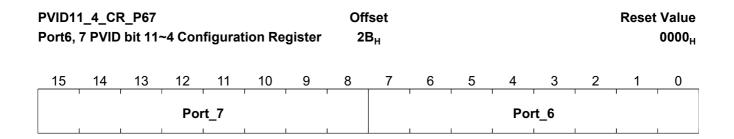

## 3.4.1.3 Address Aging